![]()

![]()

![]()

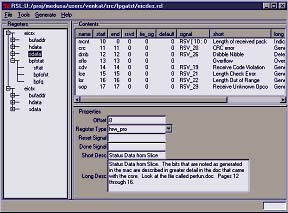

Fiesta® CRST Register Specification Tool

Benefits

Key Features

Specifications

Platforms

Fiesta® CRST is a register specification and change management tool. Manual definition of register specifications is time consuming and error-prone. Specification changes introduce further delays and increase the probability of errors due to the need for rewriting Verilog code and redoing documentation. Propagation of changes is hard to track manually.

Fiesta® CRST aids design implementation by automating the specification of registers. It automatically generates the necessary synthesizable Verilog code, verification definitions that plug into Fiesta® Open Verification Environment, C headers and documentation, dramatically speeding up design, verification, software development cycles and updating documentation, all at one go. The tool automatically propagates specification changes to all generated outputs, ensuring consistency, and further reducing the possibility of errors.

Designers will start using the tool during the micro-architecture and design phase. Changes can be easily made to the registers, with all outputs automatically regenerated. Device driver development can start as soon as the first cut register specification is done, allowing for early feedback loops.

- Intuitive Graphical User Interface promotes easy adoption and integration into design cycle

- Automatic input validations reduce errors

- Automatic generation and regeneration of directly synthesizable Verilog code dramatically compresses design cycle

- Automatic generation and regeneration of design document reduces time spent in documentation

- Automatic generation and regeneration of C headers reduces software development time

- Automatic generation and regeneration of register information useful for verification reduces verification time (in Tcl for Comit Fiesta® CVXT Open Verification Environment, or a parse-able text file)

- Direct integration into version control and release management tools like cvs and make supports version-compares

- Reusable Write-once Use-many bus interface library scheme helps build repository of reusable interface definitions

- Intuitive Graphical User Interface

- Flexible options to define a variety of bus interface libraries

- Bus interface library reusability

- Generated Verilog code suitable for synthesis and simulation

- Professional documentation output: customizable heading levels and options suitable for inclusion into MS-Word documents

- Sample instantiation templates for generated modules

- Built-in design rule checks for automatic, early detection of specification inconsistencies

- Automatic filling for unused portions of registers

- Automatic documentation facilitates good design practice

- Data format directly compatible with version control and release management tools

Inputs

- GUI based specifications for registers

Outputs

- Register bank with registers, Instantiation Template, Definitions (`defines) for easy use in other verilog sources: Verilog

- Header file definitions for each register and each bitfield - used for diagnostic software, and device driver development: C

- Verification definitions, for Comit Fiesta® CVXT, automated register read write, power up and reset tests: Tcl

- Documentation in MS-Word

Solaris (sparc) 2.7 / 2.8 (7/8) Redhat Linux 7.1 / 7.2 Windows NT4.0 / 98 / 2000/ XP

© Copyright Comit Systems, Inc. Fiesta is a registered trademark of Comit Systems, Inc. CACT, CWGT, CRST, CSMT, CVXT, CMMT, CSGT and CMBT are trademarks of Comit Systems, Inc. All other trademarks acknowledged as property of their respective trademark holders.

Industrial-strength

toolkit proven at Comit

Contract Engineering

Center

Accelerates

design cycle

Automatically generates

synthesizable Verilog

Automatically generates

documentation

Automatically

generates

verification definitions

Automatically

generates

C headers

![]()