![]()

![]()

![]()

Fiesta® CACT

System Architecture Capture ToolBenefits

Key Features

Specifications

Platforms

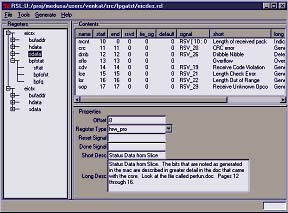

Fiesta® CACT is a VLSI design tool for architecture definition, structural design and code generation. Its graphical editor allows designers to input block level architecture, including third party IP, and generate an implementation roadmap for all modules and interfaces. The tool saves time by allowing rapid and easy definition of architectural blocks and automatically generating Verilog® and VHDL code and documentation. The Graphical User Interface (GUI) lets users add blocks in a hierarchical manner. CACT also generates system and module level block diagrams with the ability to automatically connect signals by name. CACT also makes drawing block diagrams a breeze.

- Intuitive Graphical User Interface speeds adoption

- Can use graphical input or existing code as starting point

- Generates HDL code, professional diagrams and organized documentation

- Minimizes overhead by integrating directly with version control / release management tools

- Saves design debug time by automatically embedding entity descriptions in tool outputs

- Makes explanation and understanding time, especially for code reviews, for code maintenance and transfer of technology

- Guarantees consistency between documentation and code

- Eliminates redundant information entry.

- Easy to use Graphical User Interface enables definition of connectivity as well as properties and comments for design elements

- Bus definitions enable non-cluttered schematics, even at ASIC top levels

- Imports HDL code, and infers connectivity and hierarchy information, making it easy to use the tool for existing code and for third party IP

- Automatically generates fully commented Verilog® or VHDL code. Comments include connectivity information, making debug easier

- Automatically generates professional looking vectored diagrams in Postscript and WindowsTM Metafile formats, including complete MS-Word® documentation including inline diagrams

- Automatically generates pin tables in generated documentation, reducing redundancy in user input

- ASCII database makes it easy to integrate database into version control/release management tools like cvs and Perforce.

Inputs

- Via GUI

- Import of Verilog® code

Outputs

- Verilog® code for modules

- Block diagram: .PS, .WMF

- Diagrams and Tables: .HTML, .RTF

- Complete Documentation in MS-Word format.

Solaris (sparc) 2.7 / 2.8 (7/8) Redhat Linux 7.1 / 7.2 Windows NT4.0 / 98 / 2000 / XP

© Copyright Comit Systems, Inc. Fiesta is a registered trademark of Comit Systems, Inc. CACT, CWGT, CRST, CSMT, CVXT, CMMT, CSGT and CMBT are trademarks of Comit Systems, Inc. All other trademarks acknowledged as property of their respective trademark holders.

Industrial-strength

tool proven at Comit

Contract Engineering

Center

Enables

input of block level

architecture

Accelerates

design cycle

Automatically generates

synthesizable HDL

Automatically generates

documentation

Makes

block diagrams easy

![]()